存储器之Cache相关设计原理

缓存就是存储在芯片中的内存,只不过这部分区域成本高,速度快,因此和廉价的主存区别开了。

缓存中的数据结构决定了这部分缓存起什么作用。

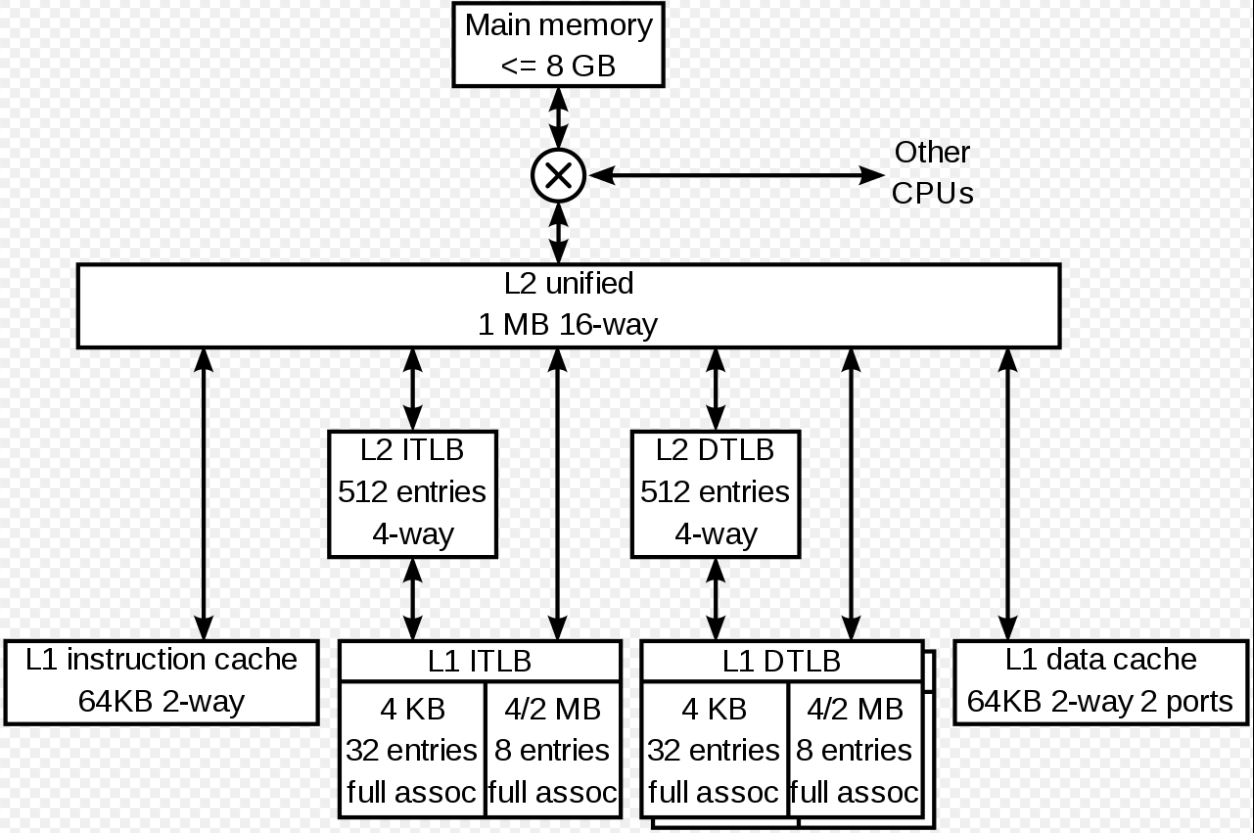

下面图来自Wiki,我觉得不错(很多CPU内部图没有tlb缓存的位置)

主存(内存)有些书以内存块表示,有些书就以(虚拟)地址表示,当内存块为1字节的时候,两者就差不多了。

地址是64位的数(建立在现代CPU情况上),如何利用这个数索引缓存块是最关键的设计步骤。

大多数缓存是分组分路的,64位地址中的其中几位(几十位)可能就用来索引组和路来找到对应的缓存块。如何分割这个数就决定了缓存的设计方式,如直接映射、组映射等等(大多数书上这样写,这部分代码是验证不了的)

参考链接

https://en.wikipedia.org/wiki/CPU_cache

https://xiangshan-doc.readthedocs.io/zh_CN/latest/memory/mmu/mmu/